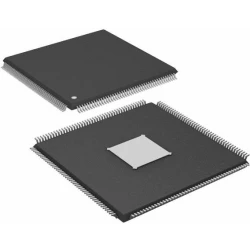

Description

AM335x Sitara™ Processors 1 Device Overview 1.1 Features 1 • Upto 1-GHz Sitara™ ARM® Cortex®-A8 32‑Bit RISC Processor– NEON™SIMDCoprocessor– 32KB of L1 Instruction and 32KB of Data Cache With Single-Error Detection (Parity)– 256KB of L2 Cache With Error Correcting Code (ECC)– 176KB of On-Chip Boot ROM– 64KB of Dedicated RAM– Emulation and Debug- JTAG– Interrupt Controller (up to 128 Interrupt Requests) • On-Chip Memory (Shared L3 RAM)– 64KB of General-Purpose On-Chip Memory Controller (OCMC) RAM– Accessible to All Masters– Supports Retention for Fast Wakeup • External Memory Interfaces (EMIF)– mDDR(LPDDR), DDR2, DDR3, DDR3L Controller:– mDDR: 200-MHz Clock (400-MHz Data Rate)– DDR2: 266-MHz Clock (532-MHz Data Rate)– DDR3: 400-MHz Clock (800-MHz Data Rate)– DDR3L: 400-MHz Clock (800-MHz Data Rate)– 16-Bit Data Bus– 1GBof Total Addressable Space– Supports One x16 or Two x8 Memory Device Configurations– General-Purpose Memory Controller (GPMC)– Flexible 8-Bit and 16-Bit Asynchronous Memory Interface With up to Seven Chip Selects (NAND, NOR, Muxed-NOR, SRAM)– Uses BCH Code to Support 4-, 8-, or 16-Bit ECC– Uses Hamming Code to Support 1-Bit ECC– Error Locator Module (ELM)– Used in Conjunction With the GPMC to Locate Addresses of Data Errors from Syndrome Polynomials Generated Using a BCH Algorithm– Supports 4-, 8-, and 16-Bit per 512-Byte Block Error Location Based on BCH Algorithms • Programmable Real-Time Unit Subsystem and Industrial Communication Subsystem (PRU-ICSS)– Supports Protocols such as EtherCAT®, 1 PROFIBUS, PROFINET, EtherNet/IP™, and More– TwoProgrammable Real-Time Units (PRUs)– 32-Bit Load/Store RISC Processor Capable of Running at 200 MHz– 8KBof Instruction RAM With Single-Error Detection (Parity)– 8KBof Data RAM With Single-Error Detection (Parity)– Single-Cycle 32-Bit Multiplier With 64-Bit Accumulator– Enhanced GPIO Module Provides ShiftIn/Out Support and Parallel Latch on External Signal– 12KB of Shared RAM With Single-Error Detection (Parity)– Three 120-Byte Register Banks Accessible by Each PRU– Interrupt Controller (INTC) for Handling System Input Events– Local Interconnect Bus for Connecting Internal and External Masters to the Resources Inside the PRU-ICSS– Peripherals Inside the PRU-ICSS:– OneUARTPort With Flow Control Pins, Supports up to 12 Mbps– OneEnhanced Capture (eCAP) Module– TwoMII Ethernet Ports that Support Industrial Ethernet, such as EtherCAT– OneMDIO Port • Power, Reset, and Clock Management (PRCM) Module– Controls the Entry and Exit of Stand-By and Deep-Sleep Modes– Responsible for Sleep Sequencing, Power Domain Switch-Off Sequencing, Wake-Up Sequencing, and Power Domain Switch-On Sequencing– Clocks– Integrated 15- to 35-MHz High-Frequenc